# Frontgrade Private RONTGRADE

# UT32M0R500 RCCA Investigation Summary: Power Up Issue

Microelectronics Division Frontgrade Technologies April 2024

Define Measure Improve Analyze Control

### **Product Information [D1]**

| FRONTGRADE |

|------------|

|------------|

| Item                  | Information                                                                         |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------|--|--|--|

| PIC #                 | QS30                                                                                |  |  |  |

| SMD #                 | 5962-17212                                                                          |  |  |  |

| UT PN                 | UT32M0R500                                                                          |  |  |  |

| Failure Mode Reported | During power-up of the uC, the device periodically does not come out of reset mode. |  |  |  |

### **Team Information [D1]**

| No. | Name                                  | Role | Title                   |

|-----|---------------------------------------|------|-------------------------|

| 1   | Bucky Young                           |      | Design Engineer         |

| 2   | Bill Clulo/Marc Pevoteaux             |      | Test Engineer           |

| 3   | Brian Baranski                        |      | System Engineer         |

| 4   | Anthony Wilson                        |      | Reliability/QA Engineer |

| 5   | Jose Betancourt/Jose Aguas/Owen Watry |      | Applications Engineer   |

| 6   | Fiona Egan                            |      | Product Engineer        |

| 7   | Robert Neubauer/Savannah Downing      |      | Validation Engineer     |

| 8   | Keith Ford                            |      | Program Manager         |

Approved for public release. Distribution is unlimited.

### Problem Description [D2]

- During power-up of the uC, the device periodically does not come out of reset mode.

- Issue is intermittent with a low occurrence rate

- Occurs under various conditions

### **Containment Actions [D3]**

| No. | <b>Containment Action Description</b>                          | Status   | Date<br>Complete | Note/Comments                                                   |

|-----|----------------------------------------------------------------|----------|------------------|-----------------------------------------------------------------|

| 1   | Trace all material shipped to affected customers to wafer lots | Complete | 13 July 2023     |                                                                 |

|     |                                                                |          |                  | All orders traced, no particular wafer/lot dependence seen      |

| 2   | Identify inventory of wafers and finished product              | Complete | 13 July 2023     | ~ 24 prototype parts in inventory for use in this investigation |

| 3   |                                                                |          |                  |                                                                 |

| 4   |                                                                |          |                  |                                                                 |

| 5   |                                                                |          |                  |                                                                 |

| 6   |                                                                |          |                  |                                                                 |

| 7   |                                                                |          |                  |                                                                 |

| 8   |                                                                |          |                  |                                                                 |

Approved for public release. Distribution is unlimited.

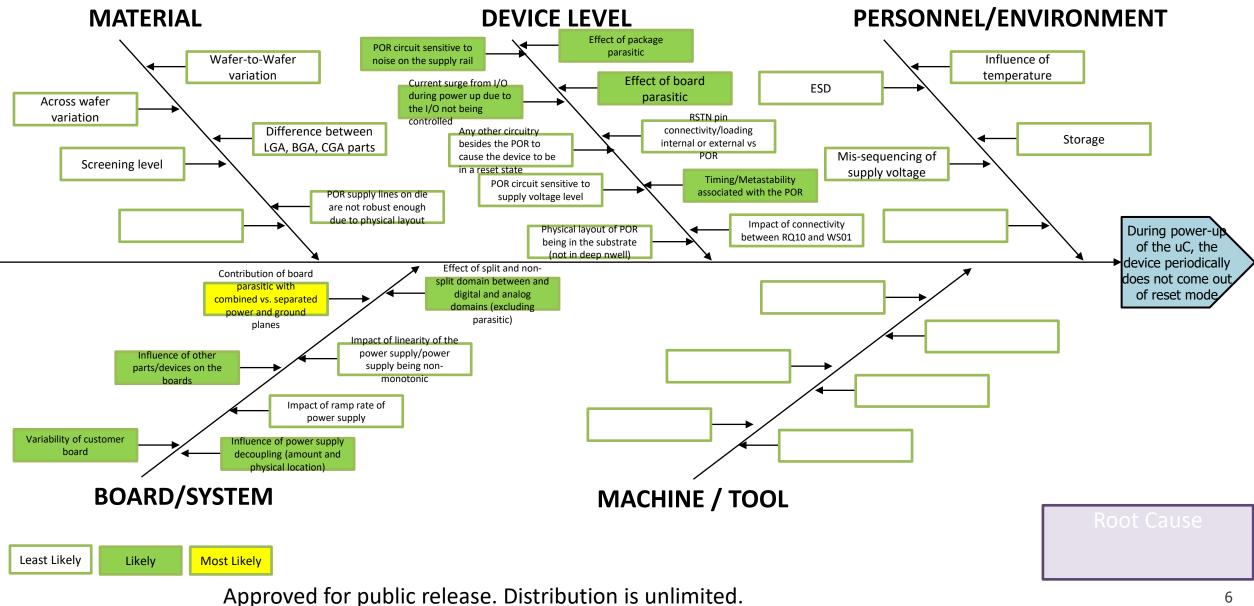

#### Frontgrade Private **Root Cause Investigation [D4]**

#### FRONTGRADE

#### **Fishbone Diagram**

### FRONTGRADE

## **Root Cause Investigation [D4]**

### Root Cause Tracking List

| Factor  | Hypothesis                                           | Likelihood   | Action                                                                           | Status    | Notes                                                                                                                                                                              |

|---------|------------------------------------------------------|--------------|----------------------------------------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |                                                      |              | 1. Simulation with device layout pkg and/or board parasitic                      |           | Simulations with parasitic extracted netlists of POR cell,<br>resistance in supply connections, package wirebond model<br>estimates. Noise added to supply voltages, repeated with |

|         | POR circuit sensitive to noise<br>on the supply rail | Likely       |                                                                                  |           | LDO regulator. Added fast large glitches to supplies.                                                                                                                              |

|         |                                                      |              | 2. Simulation with noise injection on supply                                     | Complete  | No problems found, POR function OK                                                                                                                                                 |

|         |                                                      |              | 3. Bench test with board with and without common                                 |           |                                                                                                                                                                                    |

|         |                                                      |              | ground rail with noise injection on the supply                                   | No action | Previously performed without any findings                                                                                                                                          |

|         | Current surge from I/O during                        |              |                                                                                  |           |                                                                                                                                                                                    |

|         | power up due to the I/O not                          | Likely       | 1. Investigate/document the state of the I/O during power                        |           |                                                                                                                                                                                    |

| _       | being controlled                                     |              | up                                                                               | No action | Determined to be lower rank action                                                                                                                                                 |

| e Level | Effect of package parasitic                          | Likely       |                                                                                  |           | Simulations were performed using an estimated package model.                                                                                                                       |

| vice    |                                                      |              | 1. Simulate circuit design with package parasitic                                | Complete  | No problems found, POR function OK                                                                                                                                                 |

| Device  | Timing/Metastability<br>associated with the POR      | Likely       | 1. Investigate timing sensitivity using simulation                               | Complete  | No timing issues found                                                                                                                                                             |

|         | POR circuit sensitive to supply<br>voltage level     | Least Likely |                                                                                  | No action |                                                                                                                                                                                    |

|         | POR circuit sensitive to process variation           | Least Likely | 1. Perform probing on die of various intermediate nodes within the POR circuitry | No action | No dependence seen                                                                                                                                                                 |

|         | Any other circuitry besides                          |              |                                                                                  | No action | POR_SHUTDOWN isolates POR from other circuitry                                                                                                                                     |

|         | the POR to cause the device Least I                  |              |                                                                                  |           |                                                                                                                                                                                    |

|         | to be in a reset state                               |              |                                                                                  |           |                                                                                                                                                                                    |

|         | RSTN pin connectivity/loading                        | Least Likely |                                                                                  | No action |                                                                                                                                                                                    |

|         | internal or external vs POR                          | LEAST LIKELY |                                                                                  |           |                                                                                                                                                                                    |

### FRONTGRADE

### Root Cause Tracking List

| Factor       | Hypothesis                      | Likelihood  | Action                                                           | Status   | Notes                                                                                                                  |

|--------------|---------------------------------|-------------|------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------|

|              |                                 |             | 1. Respin one of the eval boards with and without ground         |          |                                                                                                                        |

|              | Contribution of board parasitic |             | planes                                                           |          | Detailed in test section                                                                                               |

|              | with combined vs. separated     | Most Likely | 2. Shorting pins together on existing eval board                 | Complete | No problems found                                                                                                      |

|              | power and ground planes         |             | 3. Adding coupling caps between the two different grounds        |          |                                                                                                                        |

|              |                                 |             | and adding caps between the two different supply voltages        | Complete | No problems found                                                                                                      |

|              | Effect of split and non-split   |             |                                                                  |          |                                                                                                                        |

|              | domain between and digital      | Likely      |                                                                  |          |                                                                                                                        |

|              | and analog domains (excluding   | LIKCIY      | 1. Investigate the effect of difference in supply voltage levels |          | Ramped the supply voltage with no difference in POR                                                                    |

|              | parasitic)                      |             | by testing at the board level                                    | Complete | performance.                                                                                                           |

|              | Influence of other              | Likely      | 1. Investigate with a known bad part, then add or subtract       |          |                                                                                                                        |

|              | parts/devices on the boards     |             | · ·                                                              | Complete | See "QS30_RCCA_Functional_Test_Summary.docx"                                                                           |

| c            | Influence of power supply       |             | 1. Investigate adding and/or subtracting capacitance on          |          |                                                                                                                        |

| ter          | decoupling (amount and          | Likely      | supply                                                           | 1        | Analysis indicated that capacitance would have minimum impact                                                          |

| Sys          | physical location)              |             | 2. Review placement of caps on various boards                    | Complete | on issue.                                                                                                              |

| Board/System |                                 | Likely      |                                                                  |          | simulated non-linear power supply startups                                                                             |

| soa          |                                 |             |                                                                  |          | During start up time, one or two supplies dropped below detector                                                       |

|              |                                 |             |                                                                  |          | threshold & returned to high value; ran all combinations.<br>POR begins functioning over again and completes normally. |

|              | Impact of linearity of the      |             |                                                                  |          | Also, simulated combinations of supply power-up sequencing.                                                            |

|              | power supply/power supply       |             | 1. Perform power-up simulation using a non-linear supply         |          | Also, simulated combinations of supply power-up sequencing.                                                            |

|              | being non-monotonic             |             | ramp                                                             | Complete | No problems found. POR function OK.                                                                                    |

|              |                                 |             |                                                                  |          | Performed a "piece-wise" linear step of the power supply to                                                            |

|              |                                 |             |                                                                  |          | mimic a non-linear supply.                                                                                             |

|              |                                 |             | 2. Perform power-up testing in lab with non-linear supply        |          |                                                                                                                        |

|              |                                 |             | ramp                                                             | Complete | No problems found.                                                                                                     |

|              | Variability of customer board   | Likely      | · ·                                                              |          |                                                                                                                        |

|              |                                 |             |                                                                  |          | Simulation including parasitics that would mimic board were                                                            |

|              | Effect of board parasitic       | Likely      |                                                                  |          | performed. See followings slides on "Simulation                                                                        |

|              |                                 |             |                                                                  |          | Conditions/Details"                                                                                                    |

|              | Арр                             | proved fo   | r public release. Distribution is unlimited.                     |          | 8                                                                                                                      |

#### FRONTGRADE

### **Root Cause Investigation [D4]**

### Root Cause Tracking List

| Factor            | Hypothesis                                                           | Likelihood   | Action                                                               | Status    | Notes                                          |

|-------------------|----------------------------------------------------------------------|--------------|----------------------------------------------------------------------|-----------|------------------------------------------------|

|                   | Fabrication process has significant variation                        | Least Likely |                                                                      | No Action | No correlation found                           |

|                   | Wafer-to-Wafer variation                                             | Least Likely |                                                                      | No Action | No correlation found                           |

|                   | Across wafer variation                                               | Least Likely |                                                                      | No Action | No correlation found                           |

| Material          | POR supply lines on die are not robust enough due to physical layout | Least Likely |                                                                      | No Action |                                                |

|                   | Difference between LGA, BGA, and CGA                                 | Least Likely |                                                                      | No Action | No correlation found                           |

|                   | Screening Level                                                      | Least Likely | 1. Investigate ATE program for automatic power cycle per the program | Complete  | No anomalies found in test program or hardware |

| ment              | Mis-Sequencing of supply voltage causing an issue                    | Least Likely |                                                                      | No Action |                                                |

| onnel/Environment | ESD                                                                  | Least Likely |                                                                      | No Action |                                                |

|                   | Influence of temperature                                             | Least Likely |                                                                      | No Action | Characterized                                  |

| Perso             | Storage                                                              | Least Likely |                                                                      | No Action |                                                |

Simulation Conditions/Details

## **Simulations summation**

- First simulations are looking for indications of any problems; discussing that application problems for some particular devices are found to be at narrow temperature ranges

- Simulated with temperature sweeps from -50C to 120C by 10C steps

- Then repeated simulations for power-up supply ramps 0V-VDD 1ms, 10ms, 100ms

- Additional simulated with added supply noise 100kHz, 100mVpp (later 10 100MHz 100mV, 250mV)

- Results: No problems found

- Simulation of POR:

- With parasitic RC extracted

- Also added noise to supply 100kHz, 100mVpp

- Results: No problems found

Simulation Conditions/Details cont'd

- Added resistance to ground and supplies, sweeping 10, 30, 100 ohm using pex netlist, ramp supplies 0V-VDD over 1ms

- Results: No problems found, all results ok

- Inspected microcontroller physical layout for resistance in power supply connections outside the por cell, estimate < 10 ohm -- continued with series 10 ohm added into other sims

- Results ok.

- additional simulation saved signals into hierarchy at counter flip-flops. Inspecting the asynchronous clear which is asserted at beginning of reset delay for influence of noise. Added wirebond parasitics 1nH, 100mohm.

- Results ok.

Simulation Conditions/Details cont'd

- Simulated with fast ramping the supplies 0V-VDD at 10ns & 100ps

- attempting to upset the early operation & timing

- Results: Did not affect the function of reset being released after an initial power-on delay

- Checked power up sequencing with relative delay between three supplies

- Simulated six combinations, such as VDDC delayed 10ms, VDDC & VDDA delayed 10ms, etc.

- Results: No problems found.

- Simulated large & fast noise glitches on supplies during clocking

- Results: Did not change por reset function. Internal digital signals changed states, but FFs didn't latch wrong values.

#### FRONTGRADE

# Root Cause Investigation [D4]

### Simulation Conditions/Details cont'd

- Forced operating delay counters into illegal all-ones state.

- Requires overcoming triplicate redundancy and using artificial stimulus or shorting the circuitry during simulation.

- Unable to force this state using "noise" on the supplies.

- 1. if only one of three triplicated redundant LFSR counter is stuck then the POR recovers and reset is released.

- 2. if two of the three counters enters the all-ones stuck state, then the resetb is never released (and the por internal clock never stops)

- Examining the flip-flop clocks and SET-filter/buffer, adding noise 10 100MHz, 100mV, 250mV, etc. was able to cause false edges disrupting ff clocking.

- Results: POR is able to be artificially stuck by injecting/forcing internal nodes. Not able to replicate with external connections

- Simulated non-linear power supply startups

- One or two supplies dropped below detector threshold & returned to high value; ran all combinations.

- Results: POR begins functioning over again and completes normally.

- Examined the por start-up signals and FF asynchronous clear timing (powerpoint "por functional timing")

- Results: No anomalies found, POR function properly

Simulation Conditions/Details cont'd

- Simulations with LDO (powerpoint "output SR latch and clock signals")

- Added LDO regulator which supplies the internal 1.5V supply VDDC and noise to the supply. Looking for how noise may couple into the POR system externally. The regulator provides rejection, for example noise on 3.3V supply 250mV, 100MHz is reduced to ~15mV at 1.5V core supply. Added impedance at external supplies and ground.

- Results: Did not cause errors in POR function.

### FRONTGRADE

Bench Test Results

- Test procedure involved 500 power cycles per temperature, with 5 degree temperature steps from -30C to 80C. (Temperature range optimized from feedback on where customers were seeing issues)

- Anomaly was only able to be duplicated on a customer supplied board.

- New boards with a similar design and layout were fabricated but no failures were observed on these boards.

- Failing customer board was reworked (twice) with new parts that had passed on Frontgrade boards. 1 part showed no failures, second part had a low failure rate (23% at worst temperature, 1.6% over all temps)

- Original failing part on customer board did not fail on Frontgrade board.

- The bench testing demonstrated that there is some level of board interaction with the device as related to the POR anomaly but no definitive conclusions were able to be drawn.

## Material Disposition [D4]

- Material dispositioned to use "as is" with the following actions:

- Update of the datasheet to include notes on use of POR\_SHUTDOWN pin Complete

- Update of datasheet to include notes on the use of separate digital and analog ground planes – Complete

- Creating of ADEPT/GIDEP (#GB4-P-23-02) advisory of the issue and similar notes as mentioned above - Complete

## Validation [D5]

Validation of the use of the POR\_SHUTDOWN with external reset has been confirmed through bench level testing

Approved for public release. Distribution is unlimited.

### **Corrective Actions [D6]**

| No. | <b>Corrective Action Description</b>                                                 | Status   | Date<br>Complete | Note/Comments |

|-----|--------------------------------------------------------------------------------------|----------|------------------|---------------|

| 1   | Include wording in datasheet for use of the<br>POR_SHUTDOWN pin to mitigate issue    | Complete | May 07, 2024     |               |

| 2   | Include wording in datasheet for use of separate<br>analog and digital ground planes | Complete | May 07, 2024     |               |

| 3   |                                                                                      |          |                  |               |

| 4   |                                                                                      |          |                  |               |

| 5   |                                                                                      |          |                  |               |

| 6   |                                                                                      |          |                  |               |

| 7   |                                                                                      |          |                  |               |

| 8   |                                                                                      |          |                  |               |

### **Preventative Actions [D7]**

| No. | Preventative Action Description                                                                                          | Status   | Date<br>Complete | Note/Comments |

|-----|--------------------------------------------------------------------------------------------------------------------------|----------|------------------|---------------|

| 1   | Use of the POR_SHUTDOWN pin and external<br>reset will prevent issue                                                     | Complete | May 07, 2024     |               |

| 2   | Overall failure rate is low. If POR_SHUTDOWN is<br>not an option additional power cycles may be<br>required to use as is | Complete | May 07, 2024     |               |

| 3   |                                                                                                                          |          |                  |               |

| 4   |                                                                                                                          |          |                  |               |

| 5   |                                                                                                                          |          |                  |               |

| 6   |                                                                                                                          |          |                  |               |

| 7   |                                                                                                                          |          |                  |               |

| 8   |                                                                                                                          |          |                  |               |

## **Closure** [D8]

- This 8D is closed with the following:

- Issue related to anomalous behavior of the POR not coming out of reset was confirmed

- Investigation at the circuit level was performed without a "direct" link to the issue

- Various simulations were performed without a "direct" link to the issue

- Various hardware configurations were tested without a "direct" link to the issue

- Determination from the investigation is the issue has contributing factors from the design architecture interacting with the board design and board parasitic

- Recommended solution is to use the POR\_SHUTDOWN pin to mitigate the issue all together or use as is with potential for extra power cycles required.

Approved for public release. Distribution is unlimited.